Synopsys는 설계 프로세스 도구와 IP가 삼성 웨이퍼 파운드리에서 2nm 제조 공정을 준비하고 있다고 발표했습니다.삼성은 최근 2025 년에 2Nm 프로세스 반도체 칩을 대량 생산할 것이라고 발표했으며 2027 년에는 프로세스가 더욱 향상 될 것이라고 밝혔다.

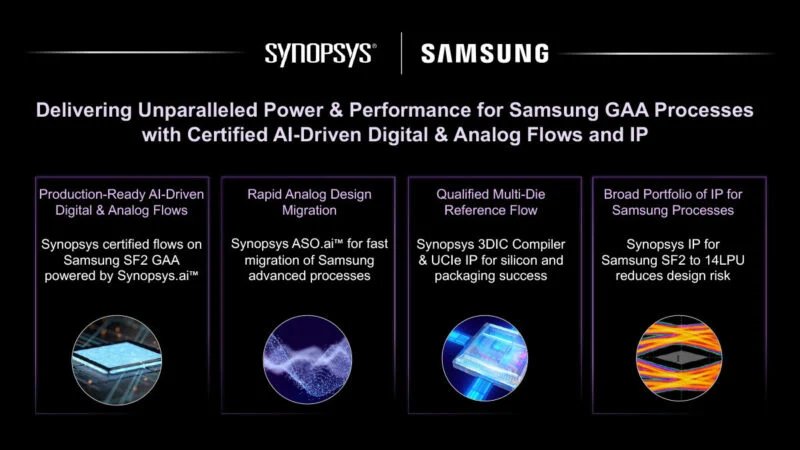

공식 소개에 따르면 Synopsys의 EDA 키트는 시뮬레이션 설계 마이그레이션, PPA (면적 효율성, 성능 및 에너지 효율) 및 삼성 웨이퍼 Foundry 2NM GAA 프로세스 노드의 생산성을 향상시킬 수 있습니다.Synopsys는 공동 최적화를 위해 인공 지능 (AI)을 활용하여 삼성이 2NM 프로세스의 지역 효율성, 성능 및 에너지 효율을 향상시킬 수 있도록 도와줍니다.

Synopsys의 DSO.AI 및 ASO.AI 도구는 FINFET에서 GAA 아키텍처로 성공적으로 마이그레이션되었습니다. 즉, 고객은 기존 Finfet 칩 설계를 새로운 2NM GAA 프로세스로 원활하게 마이그레이션 할 수 있습니다.

칩 회사는 Synopsys 도구를 사용하여 뒷면 전원 공급 배선, 로컬 레이아웃 효과 인식 방법 및 NanoSheet 장치 설계를 포함하여 새로운 칩 설계 기술을 개발하여 SF2 프로세스의 효율성 및 성능을 향상시킬 수 있습니다.삼성은 SF2Z 프로세스 노드가 성능, 전력 소비 및 밀도 (20%)를 더욱 향상시킬 수 있다고 밝혔다.

Synopsys는 또한 UCIE IP가 Samsung SF2 및 SF4X 프로세스 노드에서 칩 생산에 사용되었음을 밝혀 냈습니다.또한 동일한 DTCO 솔루션을 사용하여 삼성의 1.4NM 프로세스 노드 (SF1.4)를 최적화합니다.